- Son Dakika

- Gündem

- Ekonomi

- Finans Ekstra+

- Yazarlar

- Sektörel

- Dünya

- Kültür-Sanat

- Teknoloji

- FOTOĞRAF GALERİSİ

- VİDEO GALERİSİ

- e-Gazete

Gelişmelerden haberdar olmak için İstanbul Ticaret Haberleri uygulamasını indirin

Yapay zekânın her geçen gün daha fazla enerji talep etmesi, sürdürülebilirlik açısından yeni soruları gündeme taşıyor. Cornell Tech ve Cornell Engineering’den oluşan ekip, yapay zekâyı güçlendiren donanımı yeniden tasarlayarak bu zorluğa çözüm arıyor; hedef, hesaplamayı daha hızlı, daha verimli ve daha az enerjili kılmak. Çalışma, 1–5 Eylül tarihlerinde Hollanda’nın Leiden kentinde düzenlenen Uluslararası Alan Programlanabilir Mantık ve Uygulamalar Konferansı (FPL 2025)’te sunuldu ve En İyi Makale Ödülü ile onurlandırıldı. Makaleye arXiv ön baskı sunucusundan ulaşılabiliyor.

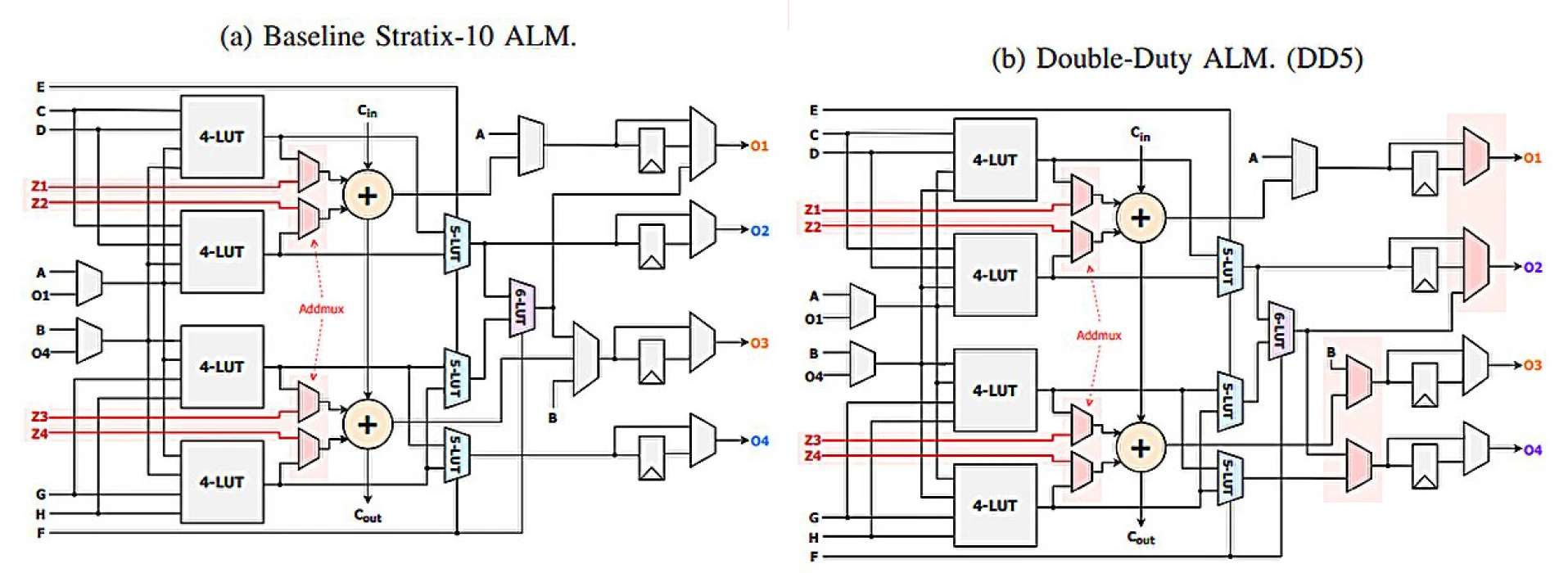

ÇİFTE GÖREV TASARIMI

Araştırma, programlanabilirliğiyle öne çıkan FPGA çiplerine odaklanıyor. Bu çipler, üretimden sonra farklı görevlere yeniden programlanabildiği için yapay zekâ, bulut bilişim ve kablosuz iletişim gibi hızla evrilen alanlarda kritik rol oynuyor. Cornell Tech’te yardımcı doçent ve ortak yazar Mohamed Abdelfattah, FPGA’ların ağ kartlarından baz istasyonlarına, tıptaki görüntüleme cihazlarından beyaz eşyaya uzanan geniş kullanımını hatırlatırken, “Yapay zekâ tüm bu cihazlara geliyor ve bu mimari bu geçişi daha verimli hale getiriyor” vurgusunu yapıyor. Geleneksel FPGA’larda LUT (Arama Tablosu) ve toplayıcı zincirleri sıkı bağlarla kısıtlı; toplayıcılara yalnızca LUT üzerinden erişilebilmesi, aritmetik yoğun AI iş yüklerinde verimliliği sınırlıyor. Double Duty mimarisi ise, aynı mantık bloğu içinde LUT ve toplayıcıların bağımsız ve eşzamanlı çalışmasına izin veriyor; böylece aynı kaynakla daha fazla iş yapılabiliyor.

VERİMLİLİK SIÇRAMASI

Bu yenilik özellikle derin sinir ağları için etkili. Sıkça FPGA’lara ‘açılır’ (donanıma gömülü sabit devre biçiminde yerleştirilir) hale getirilen bu modeller, mimari değişiklikten doğrudan fayda sağlıyor. Cornell Engineering’e de bağlı Abdelfattah, “FPGA’ların yapay zekâ hızlandırmada parladığı moda odaklandık. Küçük bir mimari dokunuşla, açılmış sinir ağlarını çok daha verimli hale getiriyor, FPGA’lara genel işlemci gibi davranmak yerine güçlü yönlerinden yararlanıyoruz” değerlendirmesini yapıyor. Testlerde Double Duty, belirli AI görevlerinde yüzde 20’nin üzerinde alan tasarrufu, geniş bir devre grubunda yaklaşık yüzde 10 performans artışı sağladı. Bu da aynı işi daha az çiple yapabilmek ve toplam enerji tüketimini düşürmek anlamına geliyor.

SANAYİDE GENİŞ UYGULAMA ALANI

Elektrik ve bilgisayar mühendisliği doktora öğrencisi ve başyazarlardan Xilai Dai, değişikliğin geleneksel endüstrilere de yarar sağladığını belirterek, “Çip doğrulama, kablosuz iletişim ve aritmetik kullanan tüm uygulamalarda daha büyük programları daha küçük çiplere sığdırarak genel verimliliği artırıyoruz” diyor. Proje, Dai’nin lisans döneminde başlattığı bir araştırma fikrinin Cornell’de tam ölçekli çalışmaya dönüşmesiyle ivme kazandı. Diğer başyazar, Cornell Tech’te eski araştırma stajyeri ve NTU mezunu Junius Pun, mimari ve modelleme çalışmalarında kilit rol üstlendi. Ekibe, Toronto Üniversitesi ve Waterloo Üniversitesi araştırmacıları ile Altera (eski Intel bölümü) mühendisleri de katıldı. Abdelfattah, “Akademi–sanayi iş birliği içinde, birçok hareketli parçayı bir araya getiren örnek bir çalışma oldu. Bu, FPGA’ları güçlü yönlerini öne çıkaracak şekilde kullanma yolunda atılmış somut bir adım” değerlendirmesini paylaşıyor.